# KA820/KA825 Processor Technical Manual

|  | · |  |

|--|---|--|

|  |   |  |

|  |   |  |

|  |   |  |

|  |   |  |

## KA820/KA825 Processor Technical Manual

#### **April 1987**

This manual is written for people who install and replace the KA825 module in the field and for people who incorporate KA825 modules into their own products or systems. The manual gives detailed information about maintenance functions. It also tells how to customize the processor and write system software, including exception handlers, interrupt handlers, and device drivers for dedicated devices.

First Edition, December 1985 Second Edition, May 1986 Third Edition, April 1987

Information in this manual is subject to change without notice and should not be construed as a commitment by Digital Equipment Corporation. Digital Equipment Corporation assumes no responsibility for any errors that may appear in this manual.

Digital Equipment Corporation makes no representation that the interconnection of its products in the manner described herein will not infringe on existing or future patent rights, nor do the descriptions contained herein imply the granting of license to make, use, or sell equipment constructed in accordance with this description.

© Digital Equipment Corporation 1985, 1986, 1987. All Rights Reserved.

Printed in U.S.A.

The following are trademarks of Digital Equipment Corporation:

DEC

DECnet

DECUS

DECsystem-10

DECSYSTEM-20

DECtape

DECUS

DECwriter

VAXELN

VAX

# **Contents**

|           |                   |                         | P                                                                                                                                                                                | age          |

|-----------|-------------------|-------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|

| Preface   |                   |                         |                                                                                                                                                                                  | хi           |

| Chapter 1 | Intr              | oductio                 | on to the KA820 Module                                                                                                                                                           |              |

|           | 1.1               | KA820                   | 0 Functional Sections                                                                                                                                                            | .1–2         |

|           |                   | 1.1.1<br>1.1.2<br>1.1.3 | CPU Section                                                                                                                                                                      | .1-2         |

|           | $\frac{1.2}{1.3}$ |                         | mer Options                                                                                                                                                                      |              |

|           |                   | $1.3.1 \\ 1.3.2$        | VAXBI AddressingVAXBI Timing and Arbitration                                                                                                                                     |              |

|           | 1.4<br>1.5<br>1.6 | Power                   | 0 Module Layout                                                                                                                                                                  | .1–6         |

| Chapter 2 | KA                | 320 Mo                  | dule Detailed Description                                                                                                                                                        |              |

|           | 2.1               | CPU S                   | Section                                                                                                                                                                          | .2–2         |

|           |                   | $2.1.1 \\ 2.1.2$        | I/E Chip Functions                                                                                                                                                               |              |

|           |                   |                         | 2.1.2.1       BTB (Backup Translation Buffer)         2.1.2.2       Cache         2.1.2.3       Internal Processor Registers         2.1.2.4       Serial-Line Units             | .2-6<br>.2-8 |

|           |                   | $2.1.3 \\ 2.1.4$        | F Chip Functions                                                                                                                                                                 |              |

|           |                   | 2.1.5                   | and the VAXBI Bus                                                                                                                                                                |              |

|           | 2.2               | VAXBI                   | I Interface                                                                                                                                                                      | 2–11         |

|           |                   | 2.2.1<br>2.2.2<br>2.2.3 | VAXBI Address Space                                                                                                                                                              | 2–13         |

|           |                   |                         | 2.2.3.1       KA820-Initiated Transactions       2.2.3.2         2.2.3.2       KA820 Slave Responses       2.2.3.3         2.2.3.3       Device Interrupt Sequence       2.2.3.3 | 2–17         |

|           | 2.3               | Port Controller and PCI Devices2–19                                                                                                                                                                         |  |  |  |

|-----------|-------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

|           |                   | 2.3.1       PCI Bus Addressing       .2-20         2.3.2       EEPROM Functions       .2-21         2.3.3       Watch Chip Interface       .2-21         2.3.4       RCX50 Controller Interface       .2-21 |  |  |  |

| Chapter 3 | Seq               | ences and Options on Power-Up                                                                                                                                                                               |  |  |  |

|           | 3.1<br>3.2<br>3.3 | Power-Up Sequence and Related Signals and Jumpers                                                                                                                                                           |  |  |  |

|           |                   | 3.3.1Power-Up Initialization.3-93.3.2Processor Initialization.3-93.3.3System Initialization.3-11                                                                                                            |  |  |  |

|           | 3.4               | Restart and Bootstrap                                                                                                                                                                                       |  |  |  |

|           |                   | 3.4.1 Restart Function (Warm Start)                                                                                                                                                                         |  |  |  |

|           |                   | 3.4.2.1 EEPROM and Boot RAM Bootstrap  Considerations                                                                                                                                                       |  |  |  |

|           | 3.5               | Sample Multiprocessor Configuration Start Sequence                                                                                                                                                          |  |  |  |

| Chapter 4 | Con               | sole Functions                                                                                                                                                                                              |  |  |  |

|           | 4.1<br>4.2        | Console States                                                                                                                                                                                              |  |  |  |

|           |                   | 4.2.1 Halt Codes                                                                                                                                                                                            |  |  |  |

|           | 4.3               | Console Commands                                                                                                                                                                                            |  |  |  |

|           |                   | $\begin{array}{cccccccccccccccccccccccccccccccccccc$                                                                                                                                                        |  |  |  |

|           | 4.4<br>4.5<br>4.6 | $ \begin{array}{llllllllllllllllllllllllllllllllllll$                                                                                                                                                       |  |  |  |

| Chapter 5 | Han        | dling Ex  | ception                                                        | s and Interrupts                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|-----------|------------|-----------|----------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|           | 5.1<br>5.2 |           |                                                                | block5–8<br>Exceptions5–8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|           |            | 5.2.1     | Machine                                                        | e-Check Stack                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|           |            |           | 5.2.1.1<br>5.2.1.2<br>5.2.1.3<br>5.2.1.4                       | Byte Count, (SP)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|           |            |           | 5.2.1.5                                                        | (SP) + 10, MTEMP.PSL.TEMP Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|           |            |           | 5.2.1.6<br>5.2.1.7<br>5.2.1.8<br>5.2.1.9<br>5.2.1.10           | $ \begin{array}{llllllllllllllllllllllllllllllllllll$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|           | 5.3<br>5.4 |           |                                                                | r Halt Considerations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Chapter 6 | Dedi       | icated I/ | O and N                                                        | Memory Devices                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|           | 6.1        | Serial-L  | ine Units                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

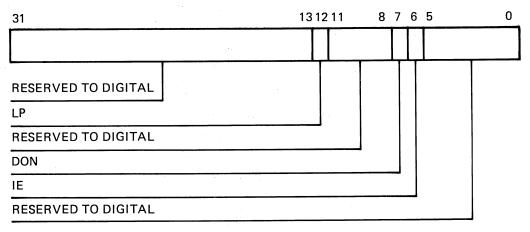

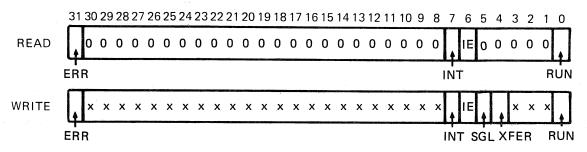

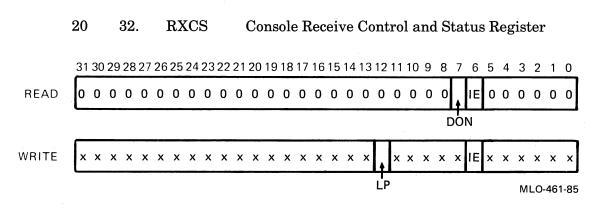

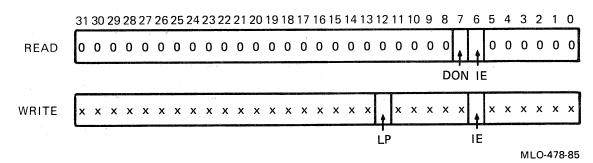

|           |            | 6.1.1     | Receive                                                        | Control and Status Registers (Read/Write) 6–3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|           |            |           | 6.1.1.1<br>6.1.1.2<br>6.1.1.3                                  | Bit ⟨12⟩ LP (Loopback Enable, Read/Write)      6-4         Bit ⟨7⟩ DON (Done, Read Only)      6-4         Bit ⟨6⟩ Interrupt Enable (Read/Write)      6-5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

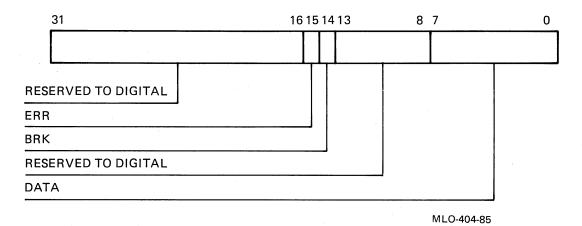

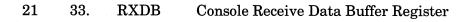

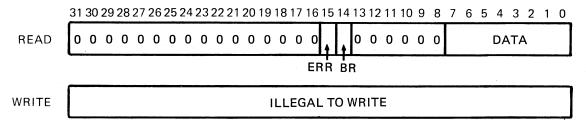

|           |            | 6.1.2     | Receive                                                        | Data Buffer Registers (Read Only)6-5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|           |            |           | 6.1.2.1<br>6.1.2.2<br>6.1.2.3                                  | Bit $\langle 15 \rangle$ ERR (Error on Received Character, Read Only)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

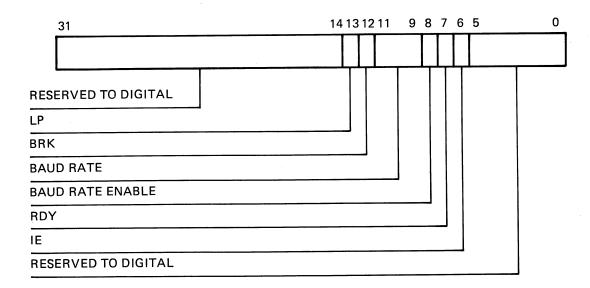

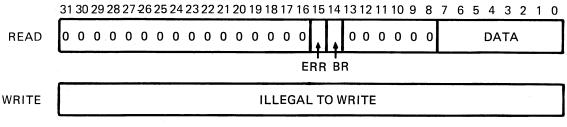

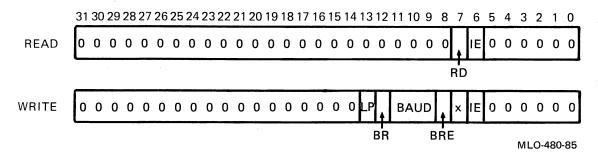

|           |            | 6.1.3     | Transmi                                                        | t Control and Status Registers (Read/Write)6-6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|           |            |           | 6.1.3.1<br>6.1.3.2<br>6.1.3.3<br>6.1.3.4<br>6.1.3.5<br>6.1.3.6 | $\begin{array}{llll} \text{Bit $\langle 13 \rangle$ LP (Loopback, Write Only)} & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & $ |

|           |            | 6.1.4     | Transmi                                                        | t Data Buffer Registers (Write Only)6-8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|           |            |           | 6.1.4.1<br>6.1.4.2                                             | Bits (11:8) of TXDB (ID Field, Write Only)6-9<br>Bits (7:0) of TXDB,<br>(Command or Transmit Data, Write Only)6-9                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|           |            |           | 6.1.4.3                                                        | Bits (7:0) of TXDB1, 2, and 3<br>(Transmit Data, Write Only)6-9                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 6.2<br>6.3<br>6.4 | Boot RA                                            | ΔM                                        | DM       .6-9          .6-11         Chip       .6-11                                                                        |

|-------------------|----------------------------------------------------|-------------------------------------------|------------------------------------------------------------------------------------------------------------------------------|

|                   | 6.4.1<br>6.4.2<br>6.4.3<br>6.4.4<br>6.4.5<br>6.4.6 | Watch C<br>Watch C<br>Watch C<br>Bootstra | hip CSR A, Address 200B 8014                                                                                                 |

| 6.5               | Control                                            | ling the R                                | CX50 Controller                                                                                                              |

|                   | 6.5.1<br>6.5.2                                     |                                           | Ansfer Examples                                                                                                              |

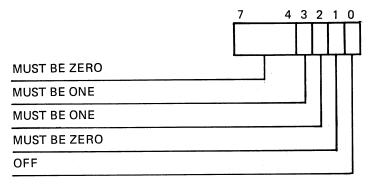

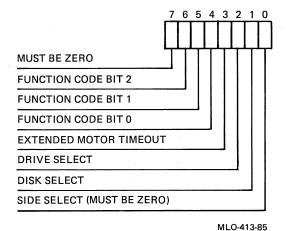

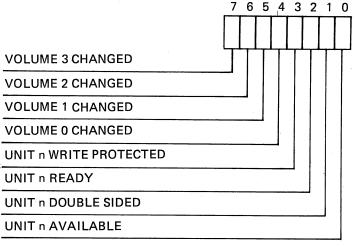

|                   |                                                    | 6.5.2.1 $6.5.2.2$                         | RX5CS0 Command Function                                                                                                      |

|                   | 6.5.3                                              | Register                                  | RX5CS1, Address 200B 0006                                                                                                    |

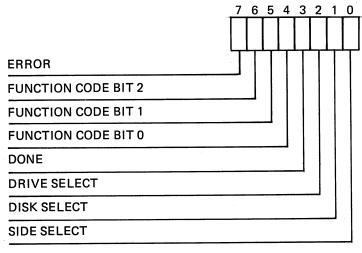

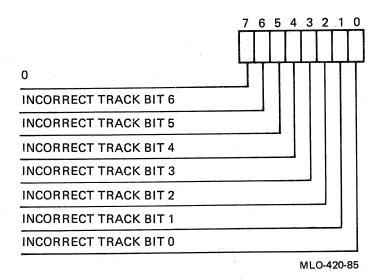

|                   |                                                    | 6.5.3.1<br>6.5.3.2                        | RX5CS1 Command Function, Track Register 6–23<br>RX5CS1 Data Transfer and<br>Maintenance Status Format, Error Register 6–24   |

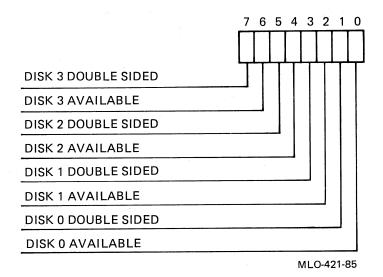

|                   | 6.5.4                                              | Register                                  | RX5CS2, Address 200B 00086–25                                                                                                |

|                   |                                                    | 6.5.4.1<br>6.5.4.2                        | RX5CS2 Data Transfer Format, Sector Register 6–25 RX5CS2 Data Transfer and Maintenance Status Format, Current Track Register |

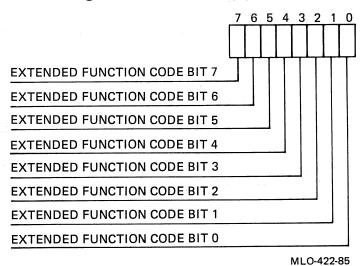

|                   | 6.5.5                                              | Register                                  | RX5CS3, Address 200B 000A                                                                                                    |

|                   |                                                    | 6.5.5.1<br>6.5.5.2                        | RX5CS3 Data Transfer Status Format, Current Sector Register                                                                  |

|                   | 6.5.6                                              | Register                                  | RX5CS4, Address 200B 000C6–28                                                                                                |

|                   |                                                    | 6.5.6.1<br>6.5.6.2                        | RX5CS4 Data Transfer Status, Incorrect Track Register                                                                        |

|                   | 6.5.7                                              | Register                                  | RX5CS5, Address 200B 000E                                                                                                    |

|                   | 6.5.8                                              | Register                                  | RX5EB, Empty Sector Buffer Register,<br>200B 0010                                                                            |

|                   | 6.5.9                                              | Register<br>Address                       | RX5CA, Clear Address Register, 200B 0012                                                                                     |

|                   | 6.5.10                                             | _                                         | RX5GO, Start Command Register, 200B 0014                                                                                     |

|                   | 6.5.11                                             | _                                         | RX5FB, Fill Sector Buffer Register,                                                                                          |

| Chapter 7  | KA820 Diagnostics                               |                                                    |                                                                                                                                                                                                             |                              |  |  |

|------------|-------------------------------------------------|----------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------|--|--|

|            | 7.1<br>7.2<br>7.3                               | Test Se                                            | athsquence and Repair Recommendations                                                                                                                                                                       | .7–3                         |  |  |

|            |                                                 | 7.3.1 $7.3.2$                                      | Booting EVKAA on the Primary Processor EVKAA Prerequisites and Functions                                                                                                                                    |                              |  |  |

|            | 7.4                                             | Using '                                            | VDS Stand-Alone                                                                                                                                                                                             | .7–5                         |  |  |

|            |                                                 | 7.4.1<br>7.4.2<br>7.4.3<br>7.4.4<br>7.4.5<br>7.4.6 | Booting VDS Stand-Alone on the Primary Processor Booting VDS Stand-Alone on an Attached Processor Help Attaching and Selecting the KA820 Module. Flags in VDS Test Repetitions.                             | .7-6<br>.7-6<br>.7-7         |  |  |

|            | 7.5<br>7.6<br>7.7<br>7.8<br>7.9<br>7.10         | EVKA<br>EVKA<br>EVKA<br>EBKA                       | VDS On-Line B, VAX Basic Instruction Exerciser C, Floating-Point Instruction Exerciser E, VAX Privileged Architecture Exerciser X, VAX 8200-Specific Cluster Exerciser N, KA820 Serial-Line Unit Diagnostic | 7–10<br>7–11<br>7–11<br>7–12 |  |  |

| Appendix A | KA820 Module I/O Pins and Cables                |                                                    |                                                                                                                                                                                                             |                              |  |  |

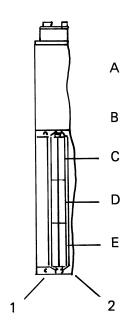

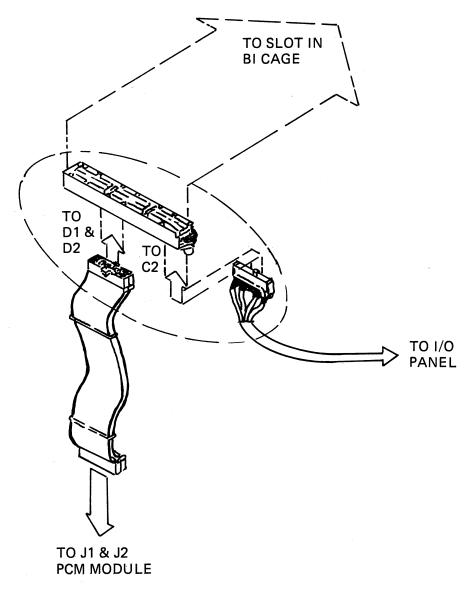

|            | A.1<br>A.2                                      |                                                    | I/O Pin Definitions                                                                                                                                                                                         |                              |  |  |

| Appendix B | Module Installation and Access to Cables        |                                                    |                                                                                                                                                                                                             |                              |  |  |

|            | B.1<br>B.2                                      |                                                    | e Installation and Replacement                                                                                                                                                                              |                              |  |  |

| Appendix C | Drive Load Characteristics of Off-Board Signals |                                                    |                                                                                                                                                                                                             |                              |  |  |

|            | C.1<br>C.2                                      |                                                    | Line Unit Signals                                                                                                                                                                                           |                              |  |  |

| Appendix D | BIIC Registers                                  |                                                    |                                                                                                                                                                                                             |                              |  |  |

|            | D.1<br>D.2<br>D.3                               | VAXBI                                              | Register, DTYPE (R/W, DMW, DCLOL)                                                                                                                                                                           | .D-2                         |  |  |

|            |                                                 | D.3.1<br>D.3.2<br>D.3.3                            | Bus Error Register Hard Error Bits                                                                                                                                                                          | .D-8                         |  |  |

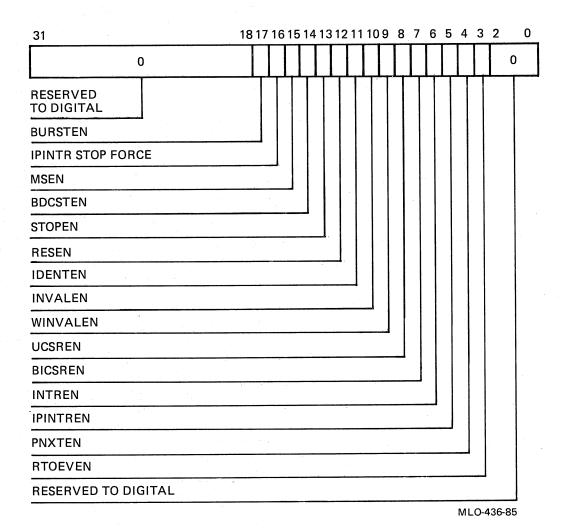

|            | D.4<br>D.5<br>D.6                               | BCI Co                                             | nterrupt Control Register, EINTRCSR                                                                                                                                                                         | D <mark>-1</mark> 0          |  |  |

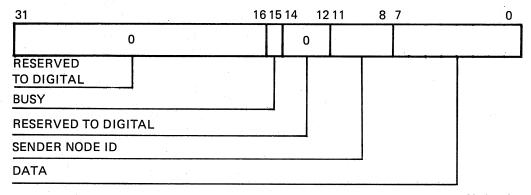

|            |                                                 | D.6.1<br>D.6.2                                     | MFPR Instruction for the RXCD Register                                                                                                                                                                      |                              |  |  |

| Appendix F | Port                                            | Contro                                             | oller Control and Status Register                                                                                                                                                                           |                              |  |  |

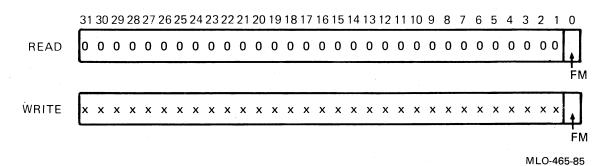

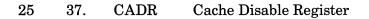

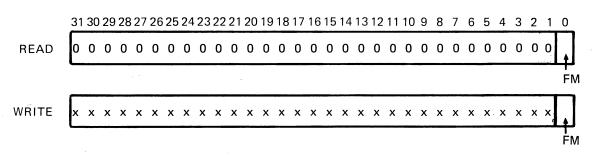

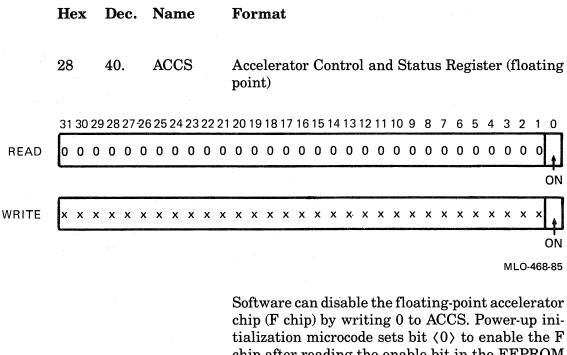

| Appendix F | Internal Processor Registers on the KA820 Module                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |  |

|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Appendix G | Register Contents at Power-Up and Boot Entry                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |

| Appendix H | EEPROM Contents                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |  |

| Appendix I | Software Boot Control Flags                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |  |

| Appendix J | Sample Bootstrap Code                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |  |

|            | J.1EEPROM Bootstrap DispatcherJ-1J.2Sample RX50 Bootstrap CodeJ-4J.3Sample DU Series Bootstrap Code (MSCP Devices)J-7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |  |

| Appendix K | Unexpected Error Conditions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |  |

|            | $ \begin{array}{llllllllllllllllllllllllllllllllllll$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |  |

| Glossary   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |  |

| Index      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |  |

| Examples   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |  |

|            | 3-1System Initialization Console Output3-123-2Loading a Patch Block into the Control-Store RAM.3-193-3Reading Control-Store Patches.3-203-4Commands to Start an Attached Processor.3-224-1Sample Console Output Following Entry to the Console Mode.4-44-2Representative Boot Commands.4-84-3Sample Console Dialog Using the D and E Commands.4-124-4Console Output Showing a Successful Slow Self-Test.4-144-5Console Output Showing a Slow Self-Test Failure.4-144-6Loading and Checking Control-Store Patches from the Console.4-214-7Logical Console Dialog Displayed on the Terminal.4-214-8Primary Processor Software Performs Logical Console Functions.4-227-1Booting EVKAA on the Primary Processor.7-47-2Booting VDS Stand-Alone on the Primary Processor.7-57-3Booting VDS On-Line from the SYSMAINT Directory.7-97-5Running VDS On-Line from RX50 Diskette Drive.7-107-6Running EBKAX.7-127-7Running EBDAN.7-13 |  |  |  |  |  |

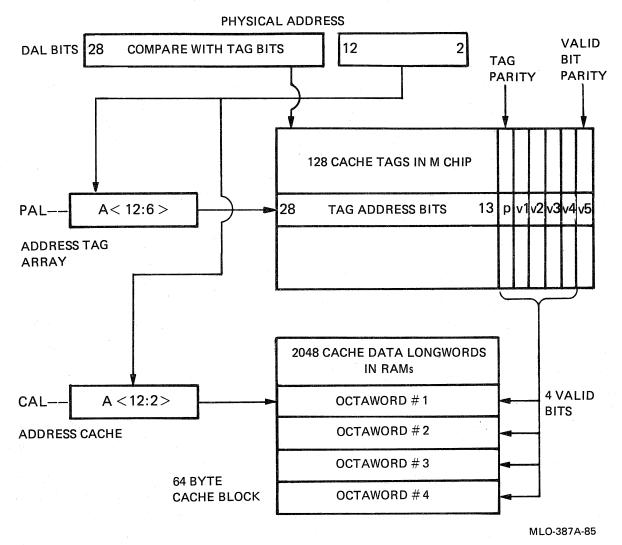

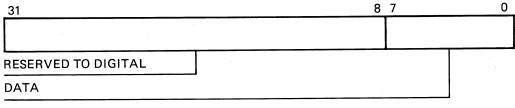

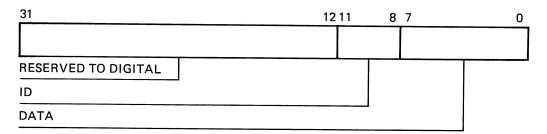

| Figures    | 1-1       KA820 Block Diagram.       .1-3         1-2       VAXBI Physical Address Space.       .1-5         1-3       KA820 Module Layout.       .1-6         2-1       KA820 CPU Section, Block Diagram       .2-3         2-2       BTB and BTB Tag Addressing       .2-5         2-3       Page Table Entry Format       .2-6         2-4       Cache and Cache Tag Addressing       .2-7         2-5       KA820 VAXBI Interface, Block Diagram       .2-11                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |  |

| 2-6    | I/O Address Space on the VAXBI Bus                               | 9_1                 |

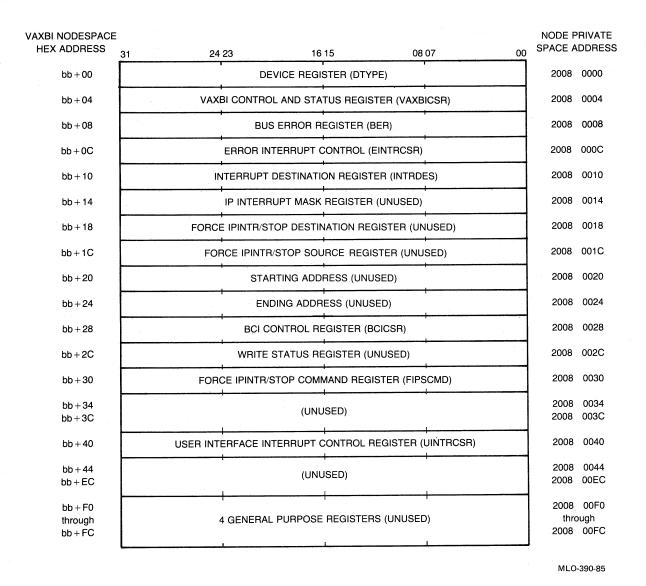

|--------|------------------------------------------------------------------|---------------------|

| 2-7    | BIIC Internal Register Addresses Used on the KA820 Module        | 2-1.<br>2 1.        |

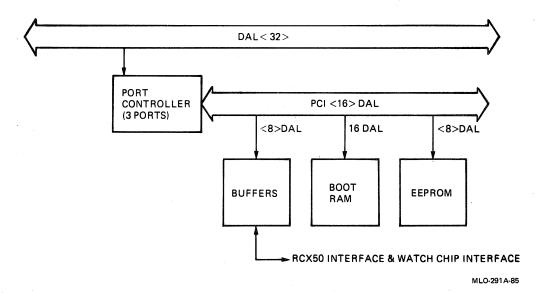

| 2-8    | Port Controller and PCI Devices, Block Diagram                   | 9_1                 |

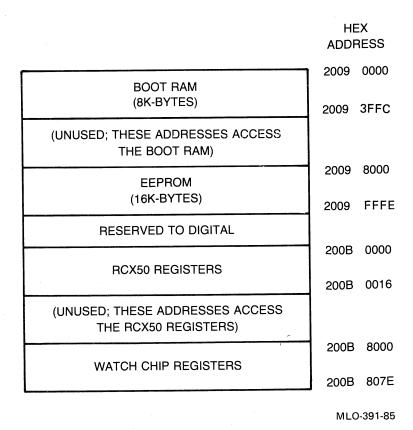

| 2-9    | PCI Device Address Map                                           | 2-1.<br>9_9         |

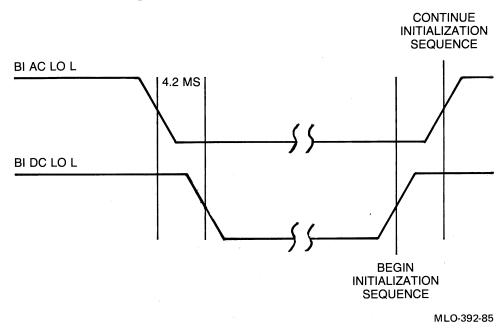

| 3–1    | BI AC LO L and BI DC LO L Sequencing.                            | <u>4</u> –2.<br>3_9 |

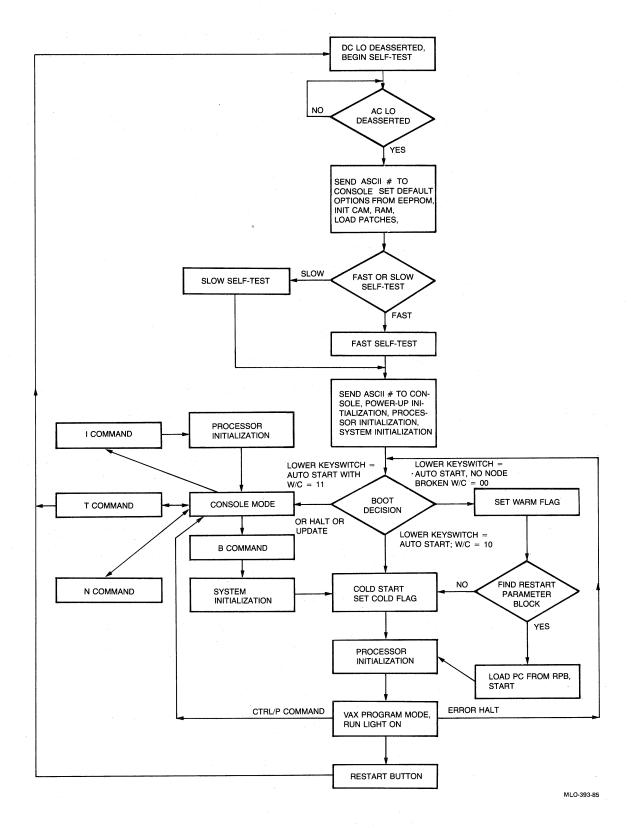

| 3-2    | Power-Up Microcode Flow                                          | 0-2<br>2_!          |

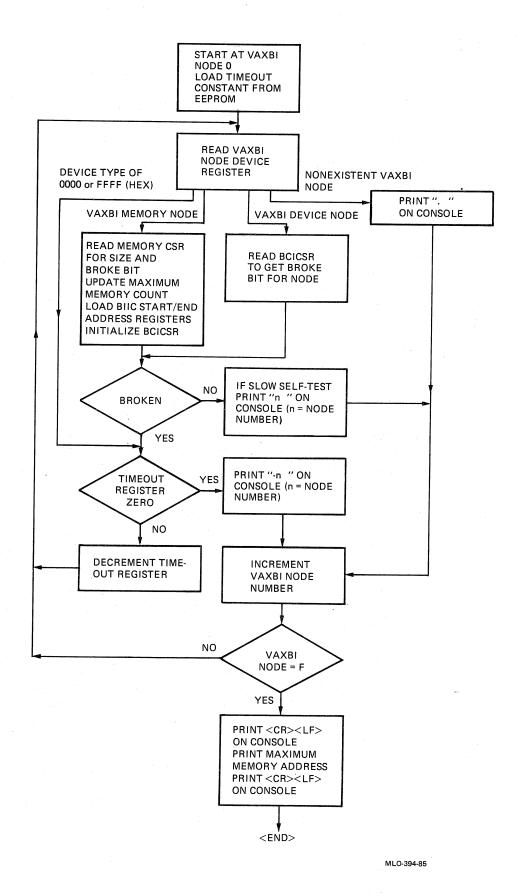

| 3 – 3  | System Initialization Sequence                                   | 3_1:                |

| 3-4    | Restart Parameter Block Format                                   | 3_1/                |

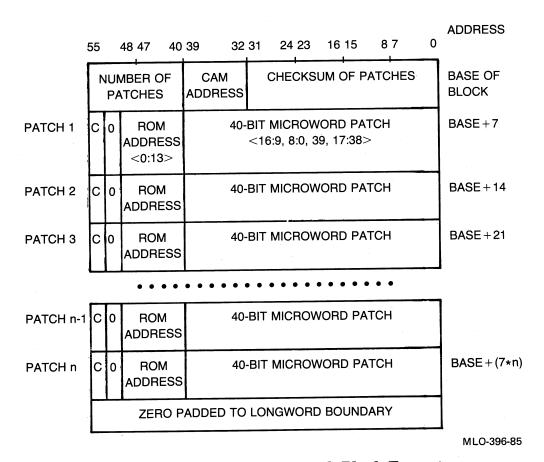

| 3-5    | Control-Store Patch Block Format                                 | 3_18                |

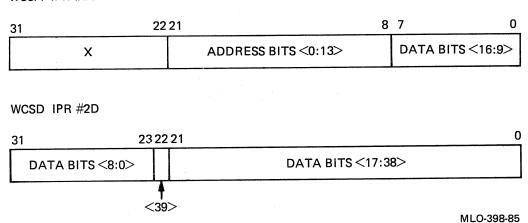

| 3-6    | WCSL Register Format                                             | 3-19                |

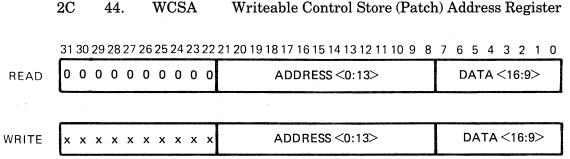

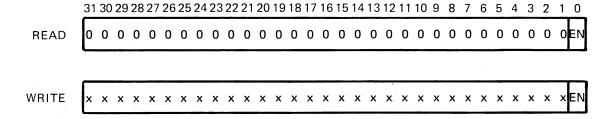

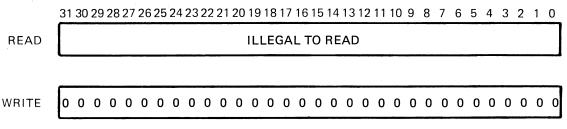

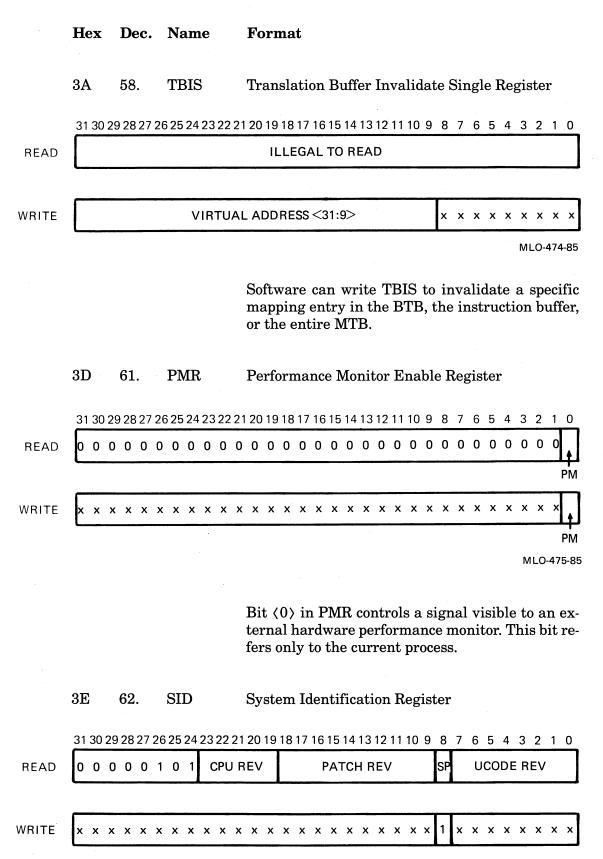

| 3-7    | WCSA and WCSD Register Formats                                   | 3-20                |

| 3–8    | Sample Multiprocessor Configuration                              | 3_91                |

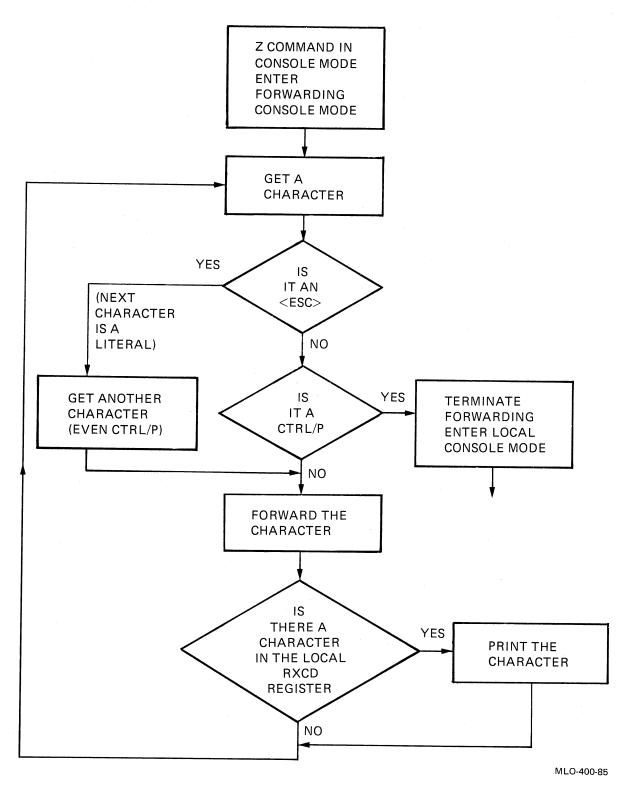

| 4–1    | Use of (ESC) with the Z Command                                  | 4_17                |

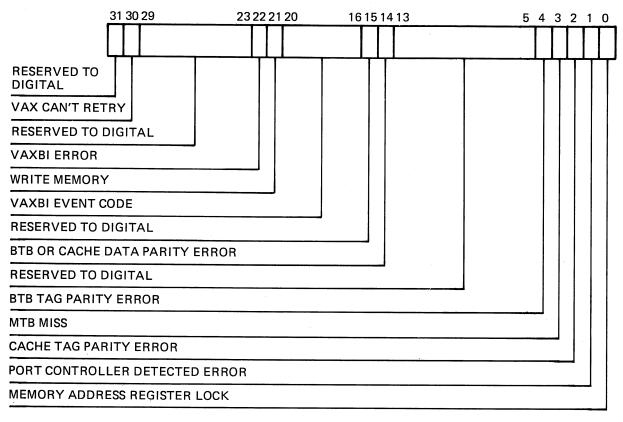

| 5-1    | Machine-Check Status Word Bit Layout                             | 5_5                 |

| 6-1    | Receive CSR Bit Format                                           | 6 /                 |

| 6-2    | Receive Data Buffer Register Format                              | 6_5                 |

| 6 - 3  | Transmit Control Status Register Format                          | 6_6                 |

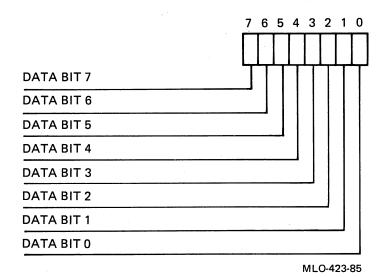

| 6-4    | Serial-Line Units 1, 2, and 3 Transmit Data Buffer (TXDB1, 2, 3) | 0-0                 |

|        | Format                                                           | 6 8                 |

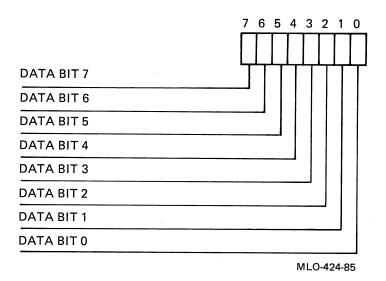

| 6-5    | Serial-Line Unit 0 Transmit Data Buffer (TXDB) Format            | 6_0                 |

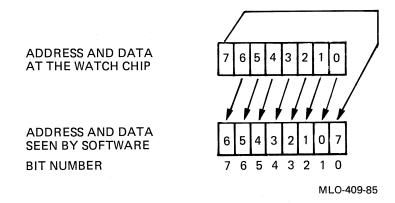

| 6-6    | Watch Chip Bit Rotation on the PCI Bus                           | 6_19                |

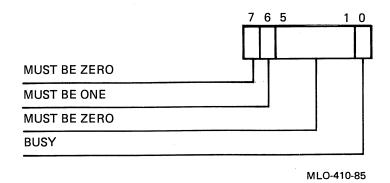

| 6-7    | Watch Chip CSR A Format                                          | 6_14                |

| 6-8    | Watch Chip CSR B Format                                          | 6_15                |

| 6–9    | Watch Chip CSR D Format                                          | 6_15                |

| 6-10   | Register RX5CS0 Command Function Format                          | 6_19                |

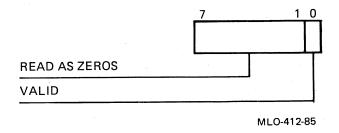

| 6-11   | Register RX5CS0 Status Format                                    | 6_22                |

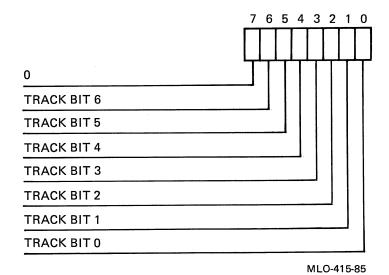

| 6-12   | RX5CS1 Command Function Format                                   | 6_23                |

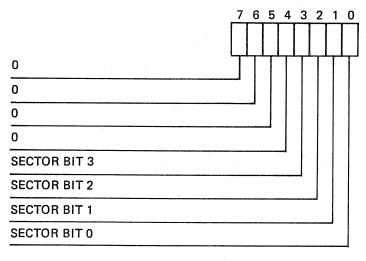

| 6-13   | RX5CS2 Command Function Format: Sector Register                  | 6_25                |

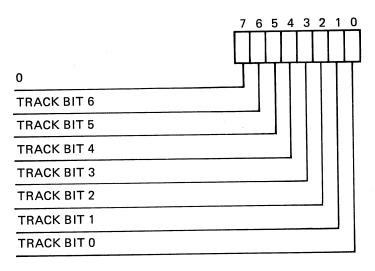

| 6-14   | RX5CS2 Status Format: Current Track Register                     | 6-26                |

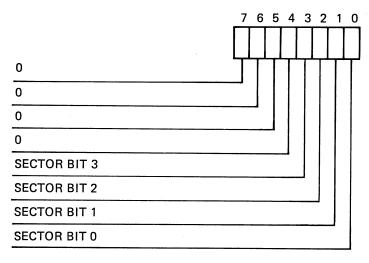

| 6-15   | RX5CS3 Data Transfer Status Format: Current Sector Register      | 6-27                |

| 6 - 16 | RX5CS3 Maintenance Status Format: Current Status Register        | 6_27                |

| 6 - 17 | RX5CS4 Command Function Format: Incorrect Track Register         | 6_28                |

| 6 - 18 | RX5CS4 Maintenance Status Format: System Configuration           | 20                  |

|        | Register                                                         | 6_29                |

| 6 - 19 | RX5CS5 Format: Extended Function                                 | 6_29                |

| 6-20   | RX5EB Format: Empty Sector Buffer Register                       | 6_30                |

| 6-21   | RX5FB Format: Fill Sector Buffer Register                        | 6_31                |

| A-1    | Module I/O Pins on Segment A Viewed from the Backplane           | υ-υ1<br>Δ_1         |

| A-2    | Module I/O Pins on Segment B Viewed from the Backplane           | $\Delta_{-9}$       |

| A-3    | Module I/O Pins on Connectors C1 and C2 Viewed from the          |                     |

|        | Backplane                                                        | Δ_9                 |

| A-4    | Module I/O Pins on Connectors D1 and D2 Viewed from the          | 11-2                |

|        | Backplane                                                        | Δ_3                 |

| A-5    | Module I/O Pins on Connectors E1 and E2 Viewed from the          | A-5                 |

|        | Backplane                                                        | ∆_Չ                 |

| A-6    | A Backplane Slot Shown from the Backplane Side of the Card Cage. | Δ 1                 |

| A-7    | Cabling for C and D Connectors                                   | Δ 5                 |

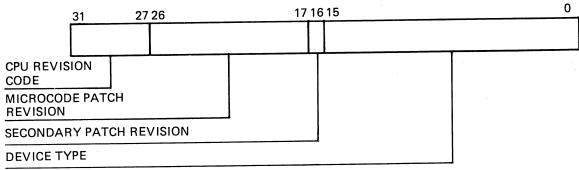

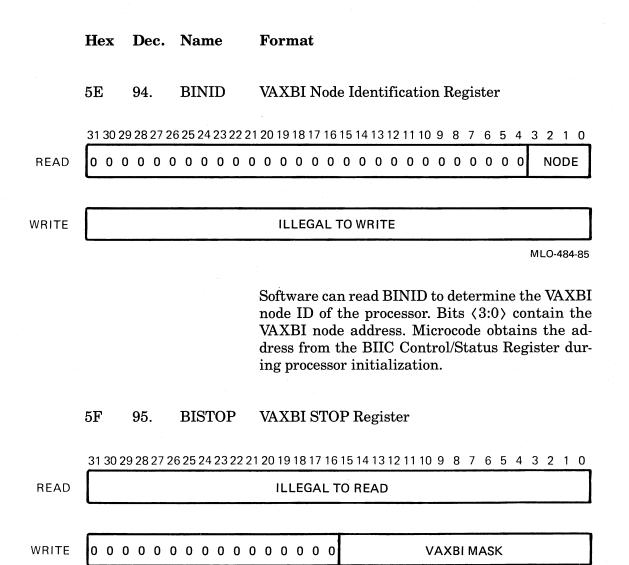

| D-1    | Device Register (DTYPE)                                          | D_9                 |

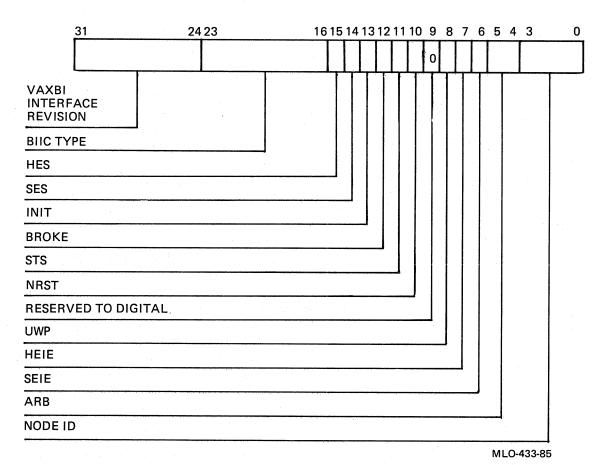

| D-2    | VAXBI Control and Status Register (VAXBICSR).                    | D_3                 |

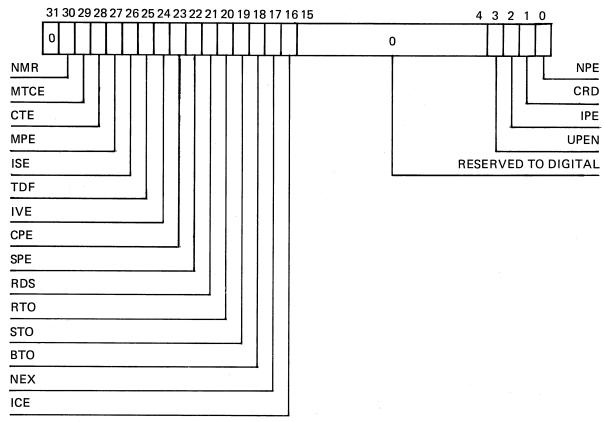

| D-3    | Bus Error Register (BER)                                         | $D_{-5}$            |

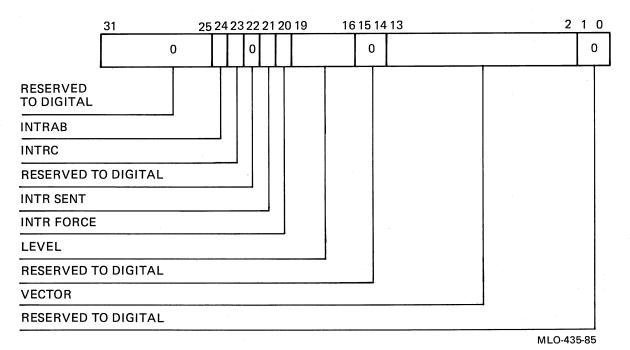

| D-4    | Error Interrupt Control Register                                 | ס-ע.                |

| D-5    | BCI Control and Status Register                                  | ה-ע<br>D 11         |

| D-6    | RXCD Register                                                    | D_ 14               |

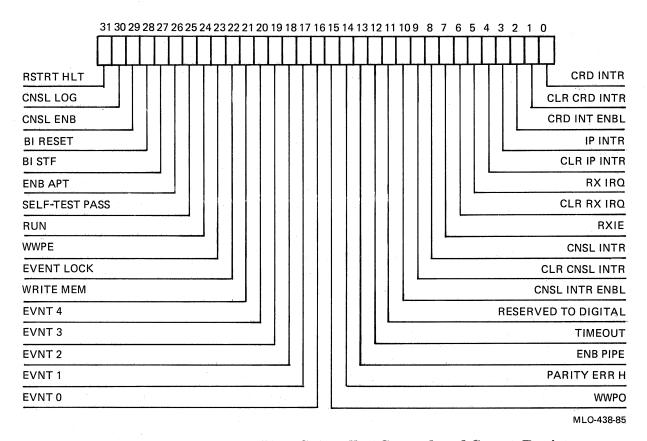

| E-1    | Port Controller Control and Status Register                      | т о<br>Т            |

#### Tables

| 1 - 1        |                                                             | .1-7   |

|--------------|-------------------------------------------------------------|--------|

| 1-2          | Environmental Requirements                                  | .1-7   |

| 2-1          | Time Required for Read and Write Data Transactions          |        |

| 2-2          | Node Space Base Address Assignments                         | 2-13   |

| 2-3          | BIIC Register Functions on the KA820 Module                 | 2 - 15 |

| 2-4          | KA820-Initiated Transactions                                | 2-16   |

| 2-5          | KA820 Slave Responses                                       | 2-18   |

| 3-1          |                                                             | .3-3   |

| 3-2          | PCM Module Jumper Configurations Affecting the              |        |

|              | EEPROM Update Function                                      | .3-4   |

| 3-3          | Slow Self-Test Checks                                       | .3-1   |

| 4–1          |                                                             | .4-2   |

| 4-2          |                                                             | .4–3   |

| 4–3          | Symbols Used in Console Command Descriptions                | .4–6   |

| 4-4          | EEPROM Customer Option Section Addresses Accessible         |        |

|              | with the D/E and E/E Commands                               | 4–11   |

| 4-5          | Console Error Codes                                         | 4-19   |

| 5-1          | Interrupt Priority Levels on the KA820 Module               | .5–2   |

| 5-2          | System Control Block Vector Assignments on the KA820 Module | 5–3    |

| 5-3          | Machine-Check Stack                                         | 5–6    |

| 5-4          | VAXBI Event Codes: Status Word Bits (20:16)                 | .5–10  |

| 6-1          | PCI Device Addresses and Accessibility                      | 6–1    |

| 6-2          | Serial-Line Unit Registers                                  | 6–3    |

| 6-3          | Setting the Baud Rate for a Serial-Line Unit                | 6–7    |

| 6-4          | EEPROM Map                                                  | .6–10  |

| 6-5          | Watch Chip Registers                                        | .6–12  |

| 6-6          | Watch Chip Data Interpretation                              | .6–13  |

| 6-7          | Watch Chip Date and Time Sample                             | .6–13  |

| 6-8          |                                                             | .6–17  |

| 6-9          | Diskette Surface Selection Code Interpretation              | .6–20  |

| 6-1          | 0 RCX50 Function Codes                                      | .6–21  |

| 6-1          | 1 RCX50 Extended Functions                                  | .6–21  |

| 6-1          | 2 RCX50 Error Codes Available in Register RX5CS1            | .6–24  |

| 7-1          | Diagnostic Program Categories Related to the VAX 8200       | 7–1    |

| 7-2          | 2 Diagnostic Programs Described in this Chapter             | 7–2    |

| C-1          |                                                             | .C-1   |

| C-2          | 2 PCI Bus Off-Board Signals                                 | C-2    |

| C-8          | 3 Other Off-Board Signals                                   | C–3    |

| $\mathbf{C}$ | Driver Output Voltages                                      | C–3    |

| $C-\xi$      | 5 Driver Output Current                                     | C–3    |

| C-6          | 6 PCI DAL (7:0) Lines Bidirectional Voltage Levels          | C-4    |

| C-'          | 7 PCI DAL (7:0) Lines Bidirectional Current Levels          | C-4    |

| C-8          |                                                             | C-4    |

| <b>D</b>     | 1 Arbitration Control Codes                                 | 1)-4   |

#### **Preface**

This manual tells what you need to know about the KA820 processor to use console commands for maintenance functions and to customize the processor to suit your needs. It also gives information you need to write system software tailored to the KA820 module, including device drivers for dedicated devices, exception handlers, and interrupt handlers.

#### **Intended Audience**

This manual is for:

- People who install and replace the KA820 module in the field.

- Engineers and system programmers who incorporate KA820 modules into their own products or systems.

#### **Before You Use This Manual**

You should be familiar with the basic concepts and features of VAX computers, including the:

- 1. VAX instruction set and data types

- 2. VAX addressing modes

- 3. VAX memory management system

- 4. VAX process structure

You can find this information in the VAX Architecture Handbook.

#### Structure of This Manual

Although the organization of this manual is tutorial, you can use the manual as a reference as well. It consists of seven chapters and a set of appendixes:

Chapter 1 Describes the major functions, characteristics, and components of the KA820 module. Together with the detailed description in Chapter 2, it gives you a context for assimilating the programming and operating information in Chapters 3 through 7.

- Chapter 2 Completes the overview begun in Chapter 1. It describes the operation of the KA820 module as a whole and explains the function of each part.

- Chapter 3 Defines the power-up functions and options available to you on the KA820 module.

- Chapter 4 Describes the console functions for the KA820. Console commands such as Examine and Boot help you to maintain the system.

- Chapter 5 Gives information you need to write exception and interrupt handling software for the KA820.

- Chapter 6 Provides programming information for the dedicated devices on the KA820 module: serial line units, boot RAM, EEPROM, watch chip, and RCX50 diskette controller.

- Chapter 7 Gives an overview of the diagnostic software that tests the KA820 and tells what you need to know to run the VAX cluster exerciser programs and the serial-line unit diagnostic program.

Appendixes A through K contain lists and tables too lengthy to include in the text of the manual. A glossary and an index follow the appendixes.

#### **Related Manuals**

The KA820 module is one of a family of processors, memories, and adapters that use the 32-bit VAXBI bus. For a technical summary of all VAXBI modules, system components, and integrated circuits see the *VAXBI Options Handbook*.

Other related technical manuals are the:

VAX 8200 Owner's Manual

MS8200 Memory Technical Description

DWBUA VAXBI-TO-UNIBUS Adapter Technical Description

VAX Architecture Handbook

VAX Diagnostic Supervisor User's Guide

VAX Diagnostic System User's Guide

#### **Conventions Used**

You form a control character by pressing the CTRL

key and typing another key at the same time.

Number bases Most numbers in the text are expressed in decimal

form. Addresses are expressed in hexadecimal form. Bit patterns are expressed in binary form. Numerals for which the context does not make the number base

clear are labeled decimal, hex, or binary.

Your input Examples show your input in red.

Uppercase Command formats show literals in uppercase.

Lowercase Command formats show variables in lowercase.

[] Command formats show optional qualifiers and

parameters enclosed in square brackets.

⟨CR⟩ Carriage return.

$\langle LF \rangle$  Line feed.

Return key. Pressing RET on the terminal sends

(CR) (LF) to the system. Most console commands terminate with (RET). The (RET) key is not shown in command examples, but you should assume that you must press (RET) after typing a command, unless the

text indicates otherwise.

Special font Text in this font indicates what you see on the console

terminal.

# Chapter 1

#### Introduction to the KA825 Module

The KA825 module is a single-board VAX processor used in the VAX 8250 and 8350 computer systems. It performs at approximately 1.2 times the speed of the VAX-11/780. A set of very large scale integrated circuits on the module implements the VAX instructions. The KA825 module communicates with other nodes in the system on the 32-bit VAXBI bus.

An earlier version of this module, the KA820, ran at approximately VAX-11/780 speed. The KA825 is distinguished by bit 23 of the System Identification Register being set. For the rest of this manual, the term KA820 refers to the KA825 module; the terms VAX 8200 and VAX 8300 refer to VAX 8250 and VAX 8350, respectively.

This introduction describes major features of the KA820 module and identifies the options available to you. Chapter 2 completes this overview and provides a background for the operating and programming details that follow.

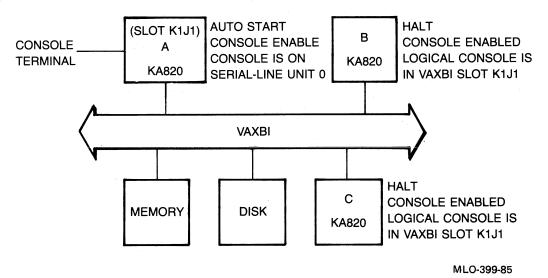

In multiprocessor systems, the first processor is called the primary processor; it is installed in VAXBI slot K1J1. Additional processors are called attached processors, and they can be installed in any slot in the VAXBI backplane. The multiprocessor system can be symmetrical, where all processors share the workload equally, or asymmetrical, where each processor is dedicated to specific functions such as I/O control or computation.

The KA820 module is designed to support three operating systems: VMS, ULTRIX-32, and VAXELN. VMS and ULTRIX-32 are general-purpose, time-sharing systems. VAXELN systems are dedicated, real-time systems developed under VMS. As a fourth alternative, you may prefer to develop your own system software for the KA820 module.

The KA820 module protects the integrity of data and processes by checking extensively for:

- Parity errors

- VAXBI transaction errors

- Unforeseen microcode conditions

- Interrupts that occur at unexpected levels

The machine-check function, which is invoked following detection of a hardware error, passes control to appropriate exception-handling software. This lets the software evaluate the situation and respond as required. In addition, the KA820 module uses a microcode-based ASCII console and provides a serial-line unit for the console terminal.

The KA820 module implements a self-test program in microcode. Self-test runs automatically on power-up and in response to a console command, and it checks the KA820 hardware thoroughly.

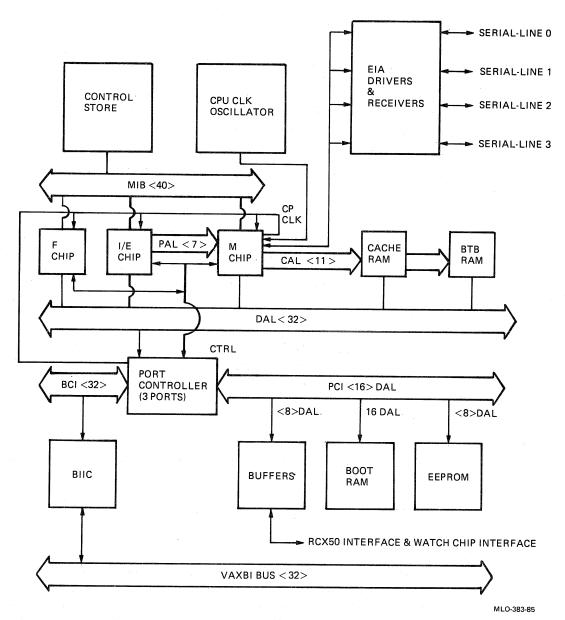

#### 1.1 KA820 Functional Sections

The KA820 module consists of three major sections:

- 1. CPU section

- 2. VAXBI interface section

- 3. Port controller and port controller interface (PCI) bus devices section

#### 1.1.1 CPU Section

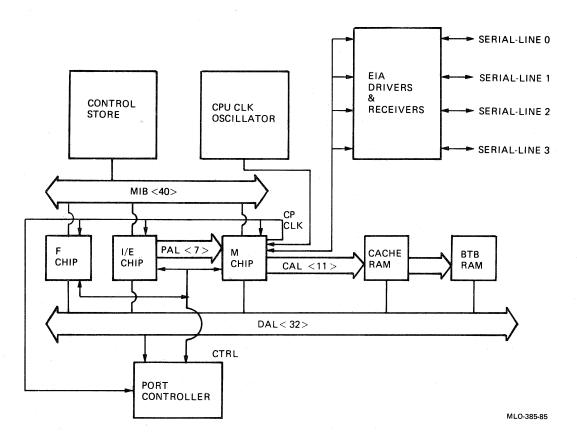

Three processor chips carry out processor functions according to 40-bit microinstructions in control store.

- I/E chip (instruction decoding and execution)

- M chip (memory management, processor registers, and four serial-line units)

- F chip (floating-point accelerator)

Control store consists of a 15K ROM and a 1K RAM implemented in five ROM/RAM chips and protected by parity. The RAM stores microcode patches, making microcode changes as simple as software changes: DIGITAL distributes microcode patches along with software updates on RX50 diskettes. The MIB bus, which connects control store and the processor chip set, is also protected by parity.

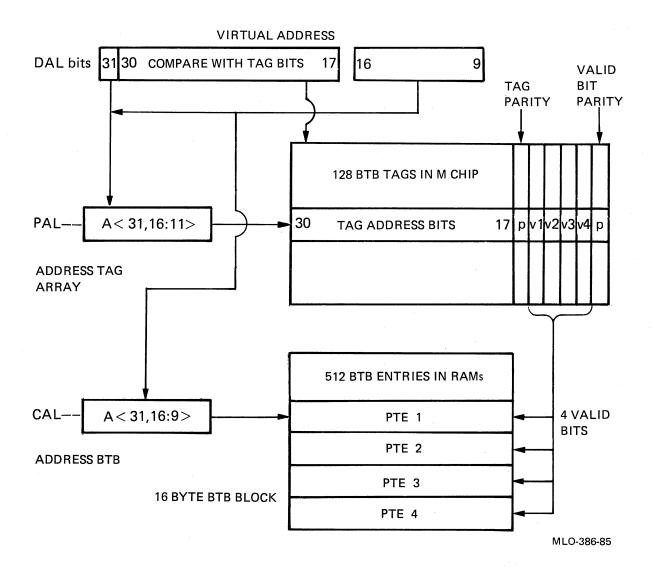

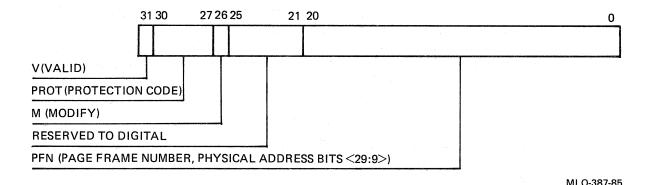

An on-board translation buffer (BTB) stores virtual-to-physical address translation information (page-table entries) for 512 pages of memory. The BTB backs up a mini-translation buffer (MTB) in the I/E chip that stores five page-table entries. And an on-board 8K-byte data cache stores data from the most recently accessed locations in memory. The processor chips communicate with the BTB and the cache on the parity-protected 32-bit DAL bus.

#### 1.1.2 VAXBI Interface Section

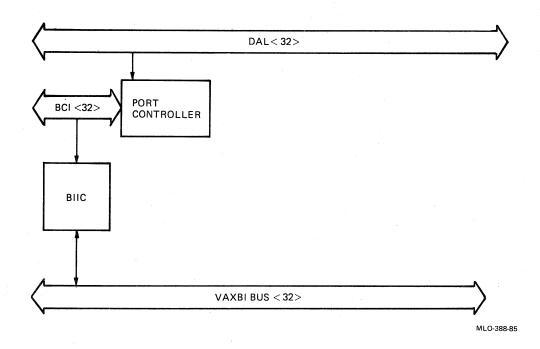

The VAXBI interface forms a second section of the KA820 module. It consists of the 32-bit, parity-protected BCI bus and the bus interconnect interface chip (BIIC). The BIIC implements the VAXBI bus protocol, including the distributed arbitration scheme and bus error checking facilities.

#### 1.1.3 Port Controller and PCI Bus Devices Section

The port controller and dedicated PCI bus devices make up a third section of the KA820 module. The port controller buffers the transfer of addresses and data between the CPU and the PCI bus devices, as well as between the CPU and the VAXBI interface.

Figure 1-1: KA820 Block Diagram

The EEPROM is a 16K-byte nonvolatile memory on the PCI bus. It stores choices for KA820 options, VAX bootstrap macrocode, and a set of patches for control-store microcode. A write-protection circuit keeps you from changing EEPROM data by mistake. Microcode copies the bootstrap macrocode to an 8K-byte boot RAM on the PCI bus at the beginning of the boot process.

The PCI bus also runs off the KA820 module to connect to the battery-backedup watch chip and the RCX50 controller for the RX5O diskette drive. The watch chip keeps the time of year for up to 100 hours without system power, and the diskette controller and drive let you install software and microcode updates.

#### 1.2 Customer Options

The KA820 module offers a variety of options that let you customize your computer system. Data stored in the EEPROM and signals that run off the module to switches on the control panel define the action and characteristics of the KA820 module on power-up:

- Perform the slow self-test or the fast self-test on power-up.

- Restart or halt on power-up following self-test.

Restart — If battery-backed-up memory has retained valid data during the preceding power outage, and no VAXBI node is faulty, try a warm start to continue the process that was executing when power failed. If memory does not contain valid data or a VAXBI node fails its self-test, boot the system, loading and starting a fresh copy of the operating system.

Halt — Enter the console mode instead of beginning program execution. In this mode, the KA820 module accepts console commands from the console terminal. Console commands are useful when you want to perform system maintenance functions such as installing software or running diagnostics.

- Set the default console baud rate to one of eight values ranging from 150 to 19200.

- Select the processor node that serves as a logical console for an attached KA820 processor in a multiprocessor system.

- Enable or disable self-test on the RCX50 diskette drive controller.

#### 1.3 VAXBI Overview

The VAXBI bus is a 32-bit synchronous bus. It joins the KA820 module to the rest of the computer system. The important characteristics of the VAXBI bus are its low cost, high bandwidth, moderate number of logical connections, large address space, and high data integrity.

All devices in the VAXBI system can arbitrate for control of the bus, so no processor is dedicated specifically to controlling bus use. Distributing the arbitration maximizes the multiprocessing capability of the bus and lets you configure systems to meet a variety of needs.

Each device on the VAXBI bus is called a node. A single VAXBI bus can have 16 nodes, which can be processors, memories, and adapters. An adapter is a node that connects other buses, communication lines, and peripheral devices to the VAXBI bus. Each of the 16 nodes can control the VAXBI bus, and slot

placement has no effect on the relative priority of the node. A node receives its priority and node ID, a number from 0 to 15 (decimal), from a plug on the VAXBI backplane slot where the node is inserted.

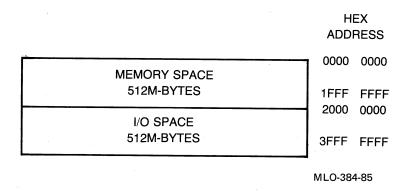

#### 1.3.1 VAXBI Addressing

The VAXBI bus supports 30-bit addressing, giving 2\*\*30 addresses (1 gigabyte of physical address space). This address space is split equally between memory and I/O space (512 megabytes each).

Figure 1-2: VAXBI Physical Address Space

In I/O space, each node has an 8K-byte block of addresses known as its nodespace. The first 256 bytes of each nodespace are allocated to registers on the BIIC. In addition, each node is allocated 3.75 megabytes of node private space. The dedicated devices on the KA820 module PCI bus use addresses in the node private space.

#### 1.3.2 VAXBI Timing and Arbitration

Events occur on the VAXBI bus at fixed intervals. Data is clocked onto the bus at the leading edge of a transmit clock signal and received and latched with a receive clock signal at the end of a bus cycle. Information processing occurs during the cycle following the one in which data is transmitted and latched.

Bus arbitration and address and data transmissions are time multiplexed over 32 data lines. Interrupt sequences use command transactions and can be directed to a single processor or to several processors. Arbitration logic is distributed among all the nodes and follows a dual round-robin priority scheme.

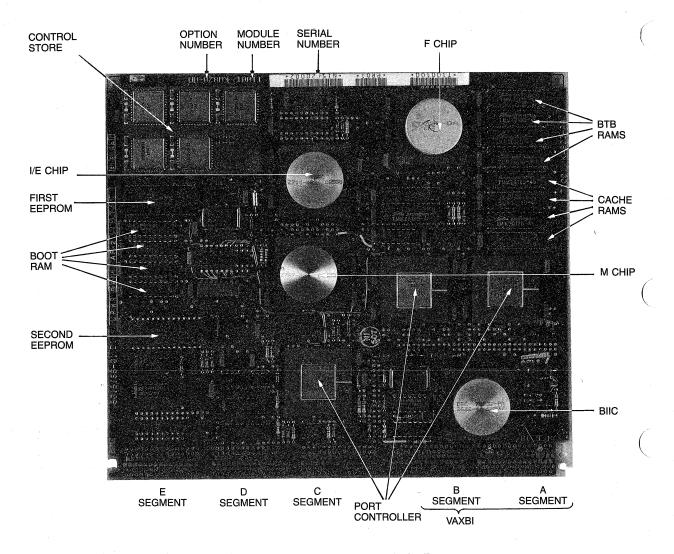

#### KA820 Module Layout

Figure 1-3 shows the major components of the KA820 module. The five segments along the bottom edge of the module provide a total of 300 external I/O pins to connect with the rest of the computer system. Segments A and B carry the VAXBI bus signals.

Figure 1-3: KA820 Module Layout

#### 1.5 Power Requirements

The KA820 module requires three voltages with the voltage regulation shown in Table 1–1. The current and power columns indicate conditions at 70 degrees C (worst case). The maximum voltage ripple is 400 millivolts peak to peak.

Table 1-1: KA820 Module Power Requirements

| Voltage | Regulation | Current      | Power            |  |

|---------|------------|--------------|------------------|--|

| +5.0    | +/- 5%     | 9.0 amps     | 45.5 watts       |  |

| +12.0   | +/- 10%    | 36 milliamps | 0.4 watts        |  |

| -12.0   | +/- 10%    | 40 milliamps | 0.5 watts        |  |

|         |            |              | 46.4 watts total |  |

## **Environmental Requirements**

The KA820 module requires air movement of at least 200 linear feet per minute, at a maximum ambient temperature of 50 degrees C. Temperature, relative humidity, and altitude requirements depend on use of the RX50 diskette drive with the KA820 module.

Table 1-2: Environmental Requirements

| Configuration                                    | Temperature                                   | Relative<br>Humidity | Altitude                        |

|--------------------------------------------------|-----------------------------------------------|----------------------|---------------------------------|

| Operation without the RX50                       | 5–50 degrees C<br>(10–122 degrees F)          | 10%-95%              | 0–2400 meters<br>(0–8000 feet)  |

| Operation with the RX50 installed and in use     | 15–32 degrees C<br>(59–90 degrees F)          | 20%-80%              | 0-2400 meters<br>(0-8000 feet)  |

| Operation with the RX50 installed but not in use | 10–40 degrees C<br>(50–104 degrees F)         | 10%–90%              | 0-2400 meters<br>(0-8000 feet)  |

| Allowable storage conditions                     | -40 to 66 degrees C<br>(-40 to 151 degrees F) | 10-95%               | 0-9000 meters<br>(0-30000 feet) |

# **Chapter 2 KA820 Module Detailed Description**

The KA820 central processor executes the full set of VAX instructions. Two address translation buffers, a data cache, and a floating-point accelerator help to make this processor efficient. The KA820 module can translate a virtual address to its physical equivalent and access cached data in 160 nanoseconds when there is a hit in the mini-translation buffer (MTB). When there is a miss in the MTB but a hit in the backup translation buffer (BTB), access to cached data requires 320 nanoseconds. In comparison, a read memory access with misses in both translation buffers and the cache requires at least 3.84 microseconds (24 CPU bus cycles).

Three functionally distinct sections make up the KA820 module:

- CPU section

- Interface to the VAXBI bus

- Port controller and related memory and I/O devices

The CPU section consists of a three-chip processor unit, control store, the backup translation buffer, and a cache. A 160-nanosecond CPU clock cycle, divided into eight phases, controls timing for the CPU section.

The BIIC (bus interconnect interface chip) coordinates the transfer of information between the KA820 module and the VAXBI bus. A separate 200-nanosecond clock cycle controls timing for the VAXBI bus.

The port controller (PCntl) acts as a buffer and traffic director, routing addresses, control signals, and data between the BIIC and the CPU section. The port controller communicates with the processor chips, the BTB, and the cache on the 32-bit DAL (data and address lines) bus. It communicates with the BIIC on the BCI bus. And it drives the 16-bit PCI, an asynchronous bus that connects the port controller to external devices as well as devices on the KA820 module:

- 8K-byte on-board boot RAM used to store bootstrap code during processor initialization

- 16K-byte on-board EEPROM that provides permanent storage for bootstrap code, control store patches, and configuration data

- RCX50 diskette controller external to the KA820 module

- Battery-backed-up watch chip external to the KA820 module

#### **CPU Section** 2.1

The KA820 module implements the VAX architecture in the CPU section, and the heart of this section is the processor chip set. The chip set consists of three custom-made, integrated circuits:

- 1. I/E chip (instruction/execution)

- 2. M chip (memory interface)

- 3. F chip (floating-point accelerator)